技术参数

| 品牌: | Texas Instruments |

| 型号: | OMAPL138AZCE3 |

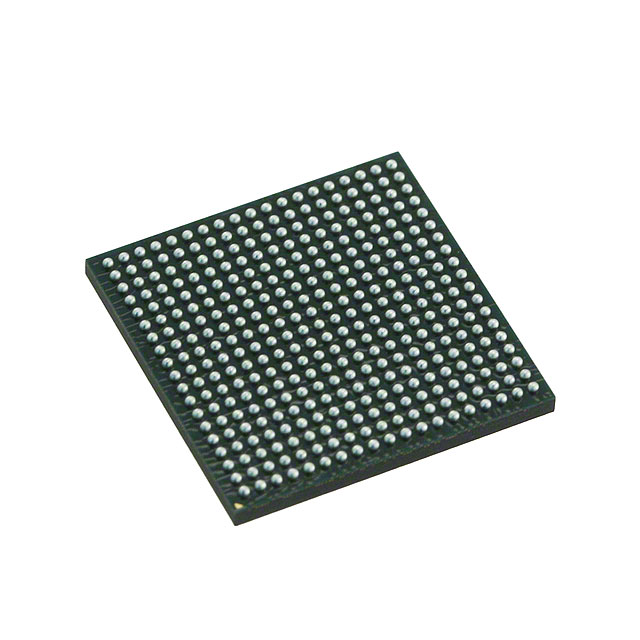

| 封装: | 361-NFBGA(13x13) |

| 批号: | 2020+ |

| 数量: | 7500 |

| 描述: | IC MPU OMAP-L1X 300MHZ 361NFBGA |

| 对无铅要求的达标情况/对限制有害物质指令(RoHS)规范的达标情况: | 无铅/符合限制有害物质指令(RoHS3)规范要求 |

| 湿气敏感性等级 (MSL): | 3(168 小时) |

| 详细描述: | ARM926EJ-S-微处理器-IC-series-1-코어-32-位-300MHz-361-NFBGA(13x13) |

| 数据列表: | OMAP-L138 Datasheet; |

| 标准包装: | 160 |

| 包装: | 托盘 |

| 零件状态: | 停產 |

| 类别: | 集成电路(IC) |

| 产品族: | 嵌入式 - 微处理器 |

| 系列: | OMAP-L1x |

| 核心处理器: | ARM926EJ-S |

| 核数/总线宽度: | 1 코어,32 位 |

| 速度: | 300MHz |

| 协处理器/DSP: | 信号处理;C674x,系统控制;CP15 |

| RAM 控制器: | SDRAM |

| 图形加速: | 无 |

| 显示与接口控制器: | LCD |

| 以太网: | 10/100Mbps(1) |

| SATA: | SATA 3Gbps(1) |

| USB: | USB 1.1 + PHY(1),USB 2.0 + PHY(1) |

| 电压 - I/O: | 1.8V,3.3V |

| 工作温度: | 0°C ~ 90°C(TJ) |

| 安全特性: | 启动安全,密码技术 |

| 封装/外壳: | 361-LFBGA |

| 供应商器件封装: | 361-NFBGA(13x13) |

OMAP-L138 C6000 DSP+ARM处理器是一款基于ARM926EJ-S和C674x DSP内核的低功耗应用处理器。该处理器提供的功率明显低于DSP的TMS320C6000TM平台的其他成员。该设备支持原始设备制造商(OEM)和原始设计制造商(ODM通过完全集成的混合处理器解决方案的最大灵活性,快速将具有强大操作系统、丰富用户界面和高处理器性能的设备推向市场。

该设备的双核架构提供了DSP和精简指令集计算机(RISC)技术的优势,结合了高性能TMS320C674x DSP内核和ARM926EJ-S内核。

ARM926EJ-S是一个32位RISC处理器核心,执行32位或16位指令并处理32位、16位或8位数据。核心使用流水线,以便处理器和内存的所有部分

系统可以连续运行。

ARM9内核有一个协处理器15(CP15)、保护模块、数据和程序内存管理单元(MMU)以及表旁视缓冲区。ARM9内核有单独的16-KB指令和16-KB数据缓存。两个高速缓存都是与虚拟索引虚拟标记(VIVT)4路关联的。ARM9内核还有8KB的RAM(矢量表)和64KB的ROM。设备DSP内核使用基于二级缓存的架构。一级程序缓存(L1P)是一个32KB的直接映射缓存,而一级数据缓存(L1D)则是一个32-KB的双向集合关联缓存。二级程序缓存(L2P)由256-KB的内存空间组成,该内存空间在程序和数据空间之间共享。L2存储器可以配置为映射存储器、高速缓存或两者的组合。尽管系统中的ARM9和其他主机可以访问DSP L2.但在不影响DSP性能的情况下,其他主机可以使用额外的128KB RAM共享存储器,Tl的基本安全引导允许用户保护专有知识产权,并防止外部实体修改用户开发的算法。通过从基于硬件的“信任根”开始,安全引导流确保了代码执行的良好起点。默认情况下,JTAG端口被锁定,以防止模拟和调试攻击;但是,JTAG端口可以在应用程序开发期间的安全引导过程中启用。引导模块在位于外部非易失性存储器(如闪存或EEPROM)中时进行加密,并在安全引导期间加载时进行解密和身份验证。加密和解密保护用户的IP,让他们安全地设置系统,并使用已知的可信代码开始设备操作。Basic Secure Boot使用SHA-1或SHA-256和AES-128进行启动映像验证,Basic SecureBoot还使用AES-128对启动映像加密。安全引导流采用多层加密方案,该方案不仅保护引导过程,还提供了安全升级引导和应用程序软件代码的能力。128位设备专用密码密钥用于保护用户加密密钥,该密钥仅为设备所知,并由NIST-800-22认证的随机数生成器生成。当需要更新时,客户会使用加密密钥创建新的加密图像。然后设备可以通过以太网等外部接口获取图像,并覆盖现有的代码。有关支持的安全功能或Tl的基本安全引导的更多详细信息,请参阅TMS320C674x/OMAP-L1x处理器安全用户指南。外围设备包括:10/100Mbps以太网媒体访问控制器(EMAC),带有管理数据输入/输出(MDIO)模块;一个USB2.0 OTG接口;一个USB1.1 0HCI接口;两个12C总线接口;一个多通道音频串行端口(McASP),带有16个串行器和FIFO缓冲器;具有FIFO缓冲器的两个多通道缓冲串行端口(McBSP);两个具有多个芯片选择的串行外围接口(SPI):一个可配置的16位主机端口接口(HPl):多达9组通用输入/输出(GPlO)引脚,每个组包含16个具有可编程中断和事件生成模式的引脚,与其他外围设备多路复用:三个UART接口(每个接口带有RTS和CTS)。两个增强型高分辨率脉宽调制器(eHRPWM)外围设备;三个32位增强捕获(eCAP)模块外围设备,可配置为3个捕获输入或3个APWM输出;两个外部存储器接口:用于慢存储器或外围设备的异步和SDRAM外部存储器接口(EMIFA);以及更高速的DDR2/Mobile DDR控制器。EMAC在设备和网络之间提供了高效的接口。EMAC同时支持10Base-T和100Base-TX,或者在半双工或全双工模式下支持10Mbps和100Mbps。此外,MDlO接口可用于PHY配置。EMAC同时支持Mll和RMll接口。串行ATA(SATA)控制器为大容量数据存储设备提供高速接口。SATA控制器同时支持SATA I(1.5 Gbps)和SATA Il(3.0 Gbps)。

通用并行端口(uPP)为许多类型的数据转换器、FPGA或其他并行设备提供高速接口。uPP支持8至16位或两个通道之间的可编程数据宽度。支持单数据速率和双数据速率传输,以及START、ENABLE.和WAlT信号,为各种数据转换器提供控制。视频端口接口(VPIF)提供了灵活的视频I/O端口。丰富的外围设备集提供了控制外部外围设备和与外部处理器通信的能力。有关每个外围设备的详细信息,请参阅本文档中的相关章节和相关的外围设备参考资料。

该设备有一套完整的ARM9和DSP开发工具,这些工具包括C编译器、简化编程和调度的DSP汇编优化器以及Windows“调试器”

用于查看源代码执行的接口。

在线客服

在线客服